## CY8C20142

# CapSense Express™ - 4 Configurable IOs

### Features

- 4 configurable IOs supporting

- CapSense buttons

- □ LED drive

- Interrupt outputs

- WAKE on interrupt input

- Bi-directional sleep control pin

- User defined Input or output

- 2.4V to 3.6V and 4.75V to 5.25V operating voltage

- Industrial temperature range: -40°C to +85°C

- I<sup>2</sup>C slave interface for configuration □ I2C data transfer rate up to 400 kbps

- Reduce BOM cost

Internal oscillator no external oscillators or crystal

Free development tool no external tuning components

- Low Operating Current

Active current:1.5 mA

Deep Sleep Current: 2.6 uA

- Available in 8-pin SOIC package

### Overview

The CapSense Express<sup>™</sup> controller allows the control of 4 IOs configurable as capacitive sensing buttons or as GPIOs for driving LEDs or interrupt signals based on various button conditions. The GPIOs are also configurable for waking up the device from sleep based on an interrupt input.

The user has the ability to configure buttons, outputs, and parameters, through specific commands sent to the  $I^2C$  port. The IOs have the flexibility in mapping to capacitive buttons and as standard GPIO functions such as interrupt output or input, LED drive and digital mapping of input to output using simple logical operations. This enables easy PCB trace routing and reduces the PCB size and stack up. CapSense Express products are designed for easy integration into complex products.

## Architecture

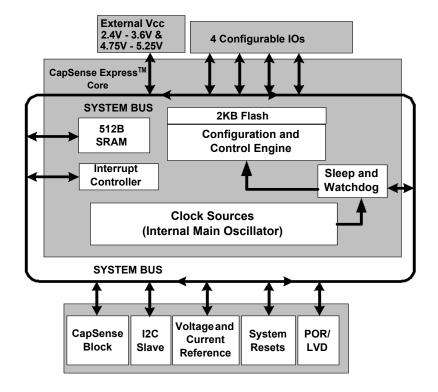

The logic block diagram shows the internal architecture of CY8C20142.

The user can configure registers with parameters needed to adjust the operation and sensitivity of the CapSense system. CY8C20142 supports a standard  $I^2C$  serial communication interface that allows the host to configure the device and to read sensor information in real time through easy register access.

## The CapSense Express Core

The CapSense Express Core has a powerful configuration and control block. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers. System resources provide additional capability, such as a configurable I<sup>2</sup>C slave communication interface and various system resets. The Analog System is composed of the CapSense PSoC block which supports capacitive sensing of up to 4 inputs.

San Jose, CA 95134-1709 • 408-943-2600 Revised July 29, 2008

## Logic Block Diagram

## Pinouts

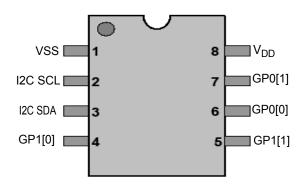

## Figure 1. Pin Diagram - 8 SOIC

#### Table 1. Pin Definitions - 8 SOIC

| Pin No | Name                 | Description                      |

|--------|----------------------|----------------------------------|

| 1      | VSS                  | Ground connection                |

| 2      | I <sup>2</sup> C SCL | I <sup>2</sup> C clock           |

| 3      | I <sup>2</sup> C SDA | I <sup>2</sup> C data            |

| 4      | GP1[0]               | Configurable as CapSense or GPIO |

| 5      | GP1[1]               | Configurable as CapSense or GPIO |

| 6      | GP0[0]               | Configurable as CapSense or GPIO |

| 7      | GP0[1]               | Configurable as CapSense or GPIO |

| 8      | VDD                  | Supply Voltage                   |

## The CapSense Analog System

The CapSense analog system contains the capacitive sensing hardware which supports CapSense Successive Approximation (CSA) algorithm. This hardware performs capacitive sensing and scanning without requiring external components. Capacitive sensing is configurable on each GPIO pin.

## Additional System Resources

System resources provide additional capability useful to complete systems. Additional resources are low voltage detection and power on reset.

- The I<sup>2</sup>C slave provides 50, 100, or 400 kHz communication over two wires.

- Low Voltage Detection (LVD) interrupts can signal the application of falling voltage levels and the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

An internal 1.8V reference provides a stable internal reference so that capacitive sensing functionality is not affected by minor  $V_{\text{DD}}$  changes.

## I<sup>2</sup>C Interface

The two modes of operation for the  $I^2C$  interface are:

- Device register configuration and status read or write for controller

- Command execution

The  $I^2C$  address is programmable during configuration. It can be locked to prevent accidental change by setting a flag in a configuration register.

## **CapSense Express Software Tool**

An easy to use software tool integrated with PSoC Express is available for configuring and tuning CapSense Express devices. Refer to the Application Note g CapSense Express devices. Refer to the Application Note "CapSense(TM) Express Software Tool - AN42137" for details of the software tool.

### CapSense Express Register Map

CapSense Express supports user configurable registers through which the device functionality and parameters are configured. For details, refer to "CY8C201xx Register Reference Guide" document.

## **Modes of Operation**

CapSense Express devices are configured to operate in any of the following three modes to meet different power consumption requirements:

- Active Mode

- Sleep Mode

- Deep Sleep Mode

## Active Mode

In the active mode, all the device blocks including the CapSense sub system are powered. Typical active current consumption of the device across the operating voltage range is 1.5 mA

## Sleep Mode

Sleep mode provides an intermediate power operation mode. It is enabled by configuring the corresponding device register. When enabled, the device enters sleep mode and wakes up after a specified sleep interval. It scans the capacitive sensors before going back to sleep again. The device can also wake up from sleep mode with a GPIO interrupt. The following sleep intervals are supported in CapSense Express. The sleep interval is configured through registers.

- 1.95 ms (512 Hz)

- 15.6 ms (64 Hz)

- 125 ms (8 Hz)

- 1S (1Hz)

## **Deep Sleep Mode**

Deep sleep mode provides the lowest power consumption because there is no operation running. In this mode, the device is woken up only using an external GPIO interrupt. A sleep timer interrupt cannot wake up a device from deep sleep mode. This can be treated as a continuous sleep mode without periodic wakeups. Refer to the Application Note "CapSense Express Power and Sleep Considerations - AN44209 for details on different sleep modes.

## **Bi-Directional Sleep Control Pin**

The CY8C20142 requires a dedicated sleep control pin to allow reliable I2C communication in case any sleep mode is enabled. This is achieved by pulling the sleep control pin LOW to wake up the device and start I2C communication. The sleep control pin can be configured on any of the GPIO. If sleep control feature is enabled, the device has one less GPIO available for CapSense/GPIO functions. The sleep control pin can also be configured as interrupt output pin from CY8C20142 to the host to acknowledge finger press on any button. To enable bi-directional feature, user has to use I2C-USB bridge program.

## **Electrical Specifications**

## Absolute Maximum Ratings

| Parameter        | Description                                                   | Min            | Тур | Max                   | Unit | Notes                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------|----------------|-----|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub> | Storage temperature                                           | -55            | 25  | +100                  | °C   | Higher storage temperatures reduce data retention time. Recommended storage temperature is $+25^{\circ}C \pm 25^{\circ}C$ (0°C to 50°C). Extended duration storage temperatures above 65°C degrade reliability. |

| T <sub>A</sub>   | Ambient temperature with power applied                        | -40            | _   | +85                   | °C   |                                                                                                                                                                                                                 |

| V <sub>DD</sub>  | Supply voltage on $V_{\text{DD}}$ relative to $V_{\text{SS}}$ | -0.5           | -   | +6.0                  | V    |                                                                                                                                                                                                                 |

| V <sub>IO</sub>  | DC input voltage                                              | $V_{SS} - 0.5$ | -   | V <sub>DD</sub> + 0.5 | V    |                                                                                                                                                                                                                 |

| V <sub>IOZ</sub> | DC voltage applied to tri-state                               | $V_{SS} - 0.5$ | -   | V <sub>DD</sub> + 0.5 | V    |                                                                                                                                                                                                                 |

| I <sub>MIO</sub> | Maximum current into any GPIO pin                             | -25            | -   | +50                   | mA   |                                                                                                                                                                                                                 |

| ESD              | Electro static discharge voltage                              | 2000           | -   | -                     | V    | Human body model ESD                                                                                                                                                                                            |

| LU               | Latch up current                                              | -              | _   | 200                   | mA   |                                                                                                                                                                                                                 |

## **Operating Temperature**

| Parameter      | Description          | Min | Тур | Max  | Unit | Notes |

|----------------|----------------------|-----|-----|------|------|-------|

| T <sub>A</sub> | Ambient temperature  | -40 | -   | +85  | °C   |       |

| TJ             | Junction temperature | -40 | -   | +100 | °C   |       |

## **DC Electrical Characteristics**

#### **DC Chip Level Specifications**

| Parameter       | Description                                                                  | Min  | Тур | Max  | Unit | Notes                                                  |

|-----------------|------------------------------------------------------------------------------|------|-----|------|------|--------------------------------------------------------|

| V <sub>DD</sub> | Supply voltage                                                               | 2.40 | -   | 5.25 | V    |                                                        |

| I <sub>DD</sub> | Supply current                                                               | -    | 1.5 | 2.5  | mA   | Conditions are $V_{DD}$ = 3.0V, $T_A$ = 25°C           |

| I <sub>SB</sub> | Deep Sleep mode current with POR<br>and LVD active. Mid temperature<br>range | _    | 2.6 | 4    | μA   | $V_{DD} = 2.55V, 0^{\circ}C \le T_{A} \le 40^{\circ}C$ |

| I <sub>SB</sub> | Deep Sleep mode current with POR and LVD active.                             | -    | 2.8 | 5    | μA   | $V_{DD} = 3.3V, -40^{\circ}C \le T_A \le 85^{\circ}C$  |

| I <sub>SB</sub> | Deep Sleep mode current with POR and LVD active.                             | -    | 5.2 | 6.4  | μA   | $V_{DD} = 5.25V, -40^{\circ}C \le T_A \le 85^{\circ}C$ |

#### 5V and 3.3V DC General Purpose IO Specifications

This table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40C $\leq$ TA $\leq$ 85C, 3.0V to 3.6V -40°C $\leq$ TA $\leq$ 85°C. Typical parameters apply to 5v and 3.3V at 25°C and are for design guidance only.

| Parameter        | Description                                                           | Min                   | Тур | Max  | Unit | Notes                                                                                                                 |

|------------------|-----------------------------------------------------------------------|-----------------------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull up resistor                                                      | 4                     | 5.6 | 8    | kΩ   |                                                                                                                       |

| V <sub>OH1</sub> | High output voltage<br>Port 0 pins                                    | V <sub>DD</sub> – 0.2 | -   | -    | V    | IOH $\leq$ 10 µA, VDD $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                        |

| V <sub>OH2</sub> | High output voltage<br>Port 0 pins                                    | V <sub>DD</sub> – 0.9 | -   | -    | V    | IOH = 1 mA, VDD $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                              |

| V <sub>OH3</sub> | High output voltage<br>Port 1 pins                                    | V <sub>DD</sub> – 0.2 | -   | -    | V    | IOH < 10 $\mu$ A, VDD $\geq$ 3.0V, maximum of 10 mA source current in all IOs.                                        |

| V <sub>OH4</sub> | High output voltage<br>Port 1 pins                                    | V <sub>DD</sub> – 0.9 | -   | -    | V    | IOH = 5 mA, VDD $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                              |

| V <sub>OH5</sub> | High output voltage<br>Port 1 pins with 3.0V LDO regulator<br>enabled | 2.75                  | 3.0 | 3.2  | V    | IOH < 10 $\mu$ A, VDD $\geq$ 3.1V, maximum of 4 IOs all sourcing 5mA.                                                 |

| V <sub>OH6</sub> | High Output Voltage<br>Port 1 pins with 3.0V LDO regulator<br>enabled | 2.2                   | -   | -    | V    | IOH = 5 mA, VDD $\geq$ 3.1V, maximum of 20 mA source current in all IOs.                                              |

| V <sub>OH7</sub> | High Output Voltage<br>Port 1 pins with 2.4V LDO regulator<br>enabled | 2.1                   | 2.4 | 2.5  | V    | IOH < 10 $\mu$ A, VDD $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                        |

| V <sub>OH8</sub> | High Output Voltage<br>Port 1 pins with 2.4V LDO regulator<br>enabled | 2                     | -   | -    | V    | IOH < 200 $\mu$ A, VDD $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                       |

| V <sub>OL</sub>  | Low output voltage                                                    | -                     | -   | 0.75 | V    | IOL = 20 mA, VDD > 3V, maximum of 60 mA<br>sink current on even port pins and 60 mA<br>sink current on odd port pins. |

| V <sub>IL</sub>  | Input low voltage                                                     | -                     | -   | 0.8  | V    | VDD = 4.75V to 5.25V.                                                                                                 |

| V <sub>IH</sub>  | Input high voltage                                                    | 2.0                   | -   | -    | V    | VDD = 4.75V to 5.25V.                                                                                                 |

| V <sub>H</sub>   | Input hysteresis voltage                                              | _                     | 140 | -    | mV   |                                                                                                                       |

| IIL              | Input leakage                                                         | -                     | 1   | -    | nA   | Gross tested to 1 µA.                                                                                                 |

| C <sub>IN</sub>  | Capacitive load on pins as input                                      | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                            |

| C <sub>OUT</sub> | Capacitive load on pins as output                                     | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C                                                                             |

#### 2.7 DC General Purpose IO Specifications

This tables lists guaranteed maximum and minimum specifications for the voltage and temperature ranges:2.4V to 3.0V and -40°C<T<sub>A</sub><85°C, respectively. Typical parameters apply to 2.7V at 25°C and are for design guidance only.

| Parameter         | Description                        | Min                   | Тур | Max  | Unit | Notes                                                                                                                                                                        |  |

|-------------------|------------------------------------|-----------------------|-----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R <sub>PU</sub>   | Pull up resistor                   | 4                     | 5.6 | 8    | kΩ   |                                                                                                                                                                              |  |

| V <sub>OH1</sub>  | High output voltage<br>Port 0 pins | V <sub>DD</sub> – 0.2 | -   | -    | V    | IOH $\leq$ 10 µA, maximum of 10 mA source current in all IOs.                                                                                                                |  |

| V <sub>OH2</sub>  | High output voltage<br>Port 0 pins | V <sub>DD</sub> – 0.5 | -   | -    | V    | IOH = 0.2 mA, maximum of 10 mA source current in all IOs.                                                                                                                    |  |

| V <sub>OH3</sub>  | High output voltage<br>Port 1 pins | V <sub>DD</sub> – 0.2 | -   | -    | V    | IOH < 10 μA, maximum of 10 mA source current in all IOs.                                                                                                                     |  |

| V <sub>OH4</sub>  | High output voltage<br>Port 1 pins | V <sub>DD</sub> – 0.5 | -   | -    | V    | IOH = 2 mA, maximum of 10 mA source current in all IOs.                                                                                                                      |  |

| V <sub>OL</sub>   | Low output voltage                 | -                     | _   | 0.75 | V    | IOL = 10 mA, maximum of 30 mA sink current<br>on even port pins (for example, P0[2] and<br>P1[4]) and 30 mA sink current on odd port<br>pins (for example, P0[3] and P1[3]). |  |

| V <sub>OLP1</sub> | Low output voltage port 1 pins     | -                     | -   | 0.4  | V    | IOL=5mA Maximum of 50mA sink current on even port pins and 50mA sink current on odd port pins. $2.4 \le V_{DD} \le 3.6V$                                                     |  |

| V <sub>IL</sub>   | Input low voltage                  | _                     | -   | 0.75 | V    | V <sub>DD</sub> = 3.0 to 3.6V                                                                                                                                                |  |

| V <sub>IH</sub>   | Input high voltage                 | 1.6                   | _   | -    | V    | V <sub>DD</sub> = 3.0 to 3.6V                                                                                                                                                |  |

| V <sub>IL</sub>   | Input low voltage                  | _                     | -   | 0.75 | V    | V <sub>DD</sub> = 2.4 to 3.6V.                                                                                                                                               |  |

| V <sub>IH1</sub>  | Input high voltage                 | 1.4                   | -   | -    | V    | V <sub>DD</sub> = 2.4 to 2.7V.                                                                                                                                               |  |

| V <sub>IH2</sub>  | Input high voltage                 | 1.6                   | -   | -    | V    | V <sub>DD</sub> = 2.7 to 3.6V                                                                                                                                                |  |

| V <sub>H</sub>    | Input hysteresis voltage           | _                     | 60  | -    | mV   |                                                                                                                                                                              |  |

| I <sub>IL</sub>   | Input leakage                      | -                     | 1   | -    | nA   | Gross tested to 1 µA.                                                                                                                                                        |  |

| C <sub>IN</sub>   | Capacitive load on pins as input   | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                                                                   |  |

| C <sub>OUT</sub>  | Capacitive load on pins as output  | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                                                                   |  |

#### 2.7V DC Spec for I2C Line with 1.8V External Pull-Up

This table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 2.4V to 3.0V and -40°C $\leq$ TA  $\leq$ 85°C, respectively. Typical parameters apply to 2.7V at 25°C. The I2C lines drive mode must be set to open drain and pulled up to 1.8V externally.

| Parameter         | Description                       | Min | Тур | Max  | Unit | Notes                                                                                                                            |

|-------------------|-----------------------------------|-----|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OLP1</sub> | Low Output Voltage Port 1 Pins    | -   | -   | 0.4  | V    | IOL=5mA Maximum of 50mA sink<br>current on even port pins and 50mA sink<br>current on odd port pins<br>$2.4 \le V_{DD} \le 3.6V$ |

| V <sub>IL</sub>   | Input low voltage                 | -   | -   | 0.75 | V    | V <sub>DD</sub> = 2.4 to 3.6V.                                                                                                   |

| V <sub>IH</sub>   | Input high voltage                | 1.4 | -   | -    | V    | V <sub>DD</sub> = 2.4 to 2.7V.                                                                                                   |

| C <sub>IN</sub>   | Capacitive load on pins as input  | 0.5 | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                       |

| C <sub>OUT</sub>  | Capacitive load on pins as output | 0.5 | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                       |

#### DC POR & LVD Specifications

| Parameter                                | Description                                                                        | Min                  | Тур                  | Max                  | Unit | Notes                                                                                                           |

|------------------------------------------|------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub> | $V_{DD}$ Value for PPOR Trip<br>$V_{DD}$ = 2.7V<br>$V_{DD}$ = 3.3V, 5V             |                      | 2.36<br>2.60         | 2.40<br>2.65         |      | $V_{DD}$ must be greater than or equal to 2.5V during startup, reset from the XRES pin, or reset from Watchdog. |

| VLVD0<br>VLVD2<br>VLVD6                  | $V_{DD}$ Value for LVD trip<br>$V_{DD}$ = 2.7V<br>$V_{DD}$ = 3.3V<br>$V_{DD}$ = 5V | 2.39<br>2.75<br>3.98 | 2.45<br>2.92<br>4.05 | 2.51<br>2.99<br>4.12 | >>>  |                                                                                                                 |

#### **DC Programming Specifications**

This table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and  $-40^{\circ}C \leq TA \leq 85^{\circ}C$ , 3.0V to 3.6V and  $-40^{\circ}C \leq TA \leq 85^{\circ}C$ , or 2.4V to 3.0V and  $-40^{\circ}C \leq TA \leq 85^{\circ}C$ , respectively. Typical parameters apply to 5V, 3.3V, or 2.7V at  $25^{\circ}C$ . These are for design guidance only. Flash Endurance and Retention specifications with the use of EEPROM user module are valid only within the range:  $25^{\circ}C \pm 20^{\circ}C$  during the Flash Write operation.

Refer to the EEPROM user module data sheet instructions for EEPROM Flash Write requirements outside the 25°C±20°C temperature window. Use of this User Module for Flash Writes outside this range must occur at a known die temperature (±20°C) and requires the designer to configure the temperature as a variable rather than the default 25°C value hard coded into the API. All use of this UM API outside the range of 25°C±20°C is at the user's own risk. This risk includes overwriting the Flash cell (when above the allowable temperature range) thereby reducing the data sheet specified endurance performance or underwriting the Flash cell (when below the allowable temperature range) thereby reducing the data sheet specified retention.

| Symbol                | Description                                                                        | Min           | Тур | Max           | Units | Notes                                |

|-----------------------|------------------------------------------------------------------------------------|---------------|-----|---------------|-------|--------------------------------------|

| Vdd <sub>IWRITE</sub> | Supply Voltage for Flash Write Operations <sup>[1]</sup>                           | 2.7           | -   | _             | V     |                                      |

| I <sub>DDP</sub>      | Supply Current During Programming or Verify                                        | -             | 5   | 25            | mA    |                                      |

| V <sub>ILP</sub>      | Input Low Voltage During Programming or<br>Verify                                  | -             | -   | 0.8           | V     |                                      |

| V <sub>IHP</sub>      | Input High Voltage During Programming or<br>Verify                                 | 2.2           | -   | -             | V     |                                      |

| I <sub>ILP</sub>      | Input Current when Applying Vilp to P1[0] or<br>P1[1] During Programming or Verify | -             | -   | 0.2           | mA    | Driving internal pull down resistor. |

| I <sub>IHP</sub>      | Input Current when Applying Vihp to P1[0] or P1[1] During Programming or Verify    | -             | -   | 1.5           | mA    | Driving internal pull down resistor. |

| V <sub>OLV</sub>      | Output Low Voltage During Programming or<br>Verify                                 | _             | _   | Vss +<br>0.75 | V     |                                      |

| V <sub>OHV</sub>      | Output High Voltage During Programming or Verify                                   | Vdd<br>-1.0   | -   | Vdd           | V     |                                      |

| Flash <sub>ENPB</sub> | Flash Endurance (per block)                                                        | 50,000        | -   | -             | -     | Erase/write cycles per block.        |

| Flash <sub>ENT</sub>  | Flash Endurance (total)                                                            | 1,800,0<br>00 | -   | -             | -     | Erase/write cycles.                  |

| Flash <sub>DR</sub>   | Flash Data Retention                                                               | 10            | _   | _             | Years |                                      |

## **Capsense Electrical Characteristics**

| Max (V) | Typical (V) | Min (V) | Low Voltage Cutoff (V) | Notes                 |

|---------|-------------|---------|------------------------|-----------------------|

| 5.25    | 5.0         | 4.75    | 4.73                   | See notes [5] and [6] |

| 3.6     | 3.3         | 3.02    | _                      | See note [2]          |

| 3.02    | 2.7         | 2.45    | 2.45                   | See notes [3] and [4] |

Notes

Commands involving Flash Writes (0x01, 0x02, 0x03) must be executed only within the same VCC voltage range detected at POR (power on, XRES, or command 0x06) and above 2.7V. For register details, refer to CY8C201xx Register Reference Guide. If the user powers up the device in the 2.4V–3.6V range, Flash writes must be performed only between 2.7V and 3.6V. If the user powers up the device in the 4.75V–5.25V range, Flash writes must be performed in that range only.

If the device is in 3.3V mode of operation and the operating voltage drops below 3.02V, the device automatically reconfigure's itself to work in 2.7V mode of operation.

If the device is in 2.7V mode of operation and the operating voltage drops below 2.45V, the scanning for Capsense parameters shuts down until the voltage returns to over 2.45V. If the voltage continues to drop and goes below 2.4V, device goes into reset.

If the device is in 2.7V mode of operation and the operating voltage rises above 3.02V, the device automatically reconfigure's itself to work in 3.3V mode of operation.

If the device is in 5.0V mode of operation and the operating voltage drops below 4.73V, the scanning for Capsense parameters shuts down until the voltage returns to over 4.73V.

Powering up in the 3.6V to 4.75V range is not supported by Capsense Express. The device initializes to the 5.0V parameters but does not enable Capsense scanning until the voltage goes above 4.73V.

## **AC Electrical Specifications**

## 5V and 3.3V AC General Purpose IO Specifications

| Parameter | Description                                         | Min | Max | Unit | Notes                                                           |

|-----------|-----------------------------------------------------|-----|-----|------|-----------------------------------------------------------------|

| TRise0    | Rise time, strong mode,<br>Cload = 50 pF, Port 0    | 15  | 80  | ns   | V <sub>DD</sub> = 3.0V to 3.6V and 4.75V to 5.25V,<br>10% - 90% |

| TRise1    | Rise time, strong mode,<br>Cload = 50 pF, Port 1    | 10  | 50  | ns   | V <sub>DD</sub> = 3.0V to 3.6V, 10% - 90%                       |

| TFall     | Fall time, strong mode,<br>Cload = 50 pF, all ports | 10  | 50  | ns   | V <sub>DD</sub> = 3.0V to 3.6V and 4.75V to 5.25V,<br>10% - 90% |

#### 2.7V AC General Purpose IO Specifications

| Parameter | Description                                         | Min | Max | Unit | Notes                                     |

|-----------|-----------------------------------------------------|-----|-----|------|-------------------------------------------|

| TRise0    | Rise time, strong mode,<br>Cload = 50 pF, Port 0    | 15  | 100 | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

| TRise1    | Rise time, strong mode,<br>Cload = 50 pF, Port 1    | 10  | 70  | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

| TFall     | Fall time, strong mode,<br>Cload = 50 pF, all ports | 10  | 70  | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

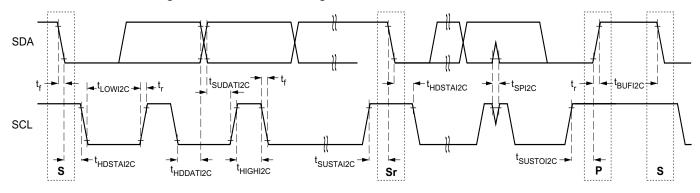

## AC I<sup>2</sup>C Specifications

| Parameter                           | Description                                                                                  | Standard<br>Mode |     | Fast Mode |     | Units | Notes                                                 |

|-------------------------------------|----------------------------------------------------------------------------------------------|------------------|-----|-----------|-----|-------|-------------------------------------------------------|

|                                     |                                                                                              | Min              | Max | Min       | Max |       |                                                       |

| F <sub>SCL</sub> I <sup>2</sup> C   | SCL clock frequency                                                                          | 0                | 100 | 0         | 400 | kbps  | Fast mode not supported for<br>V <sub>DD</sub> < 3.0V |

| T <sub>HDSTA</sub> I <sup>2</sup> C | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4.0              | _   | 0.6       | -   | μs    |                                                       |

| T <sub>LOW</sub> I <sup>2</sup> C   | LOW period of the SCL clock                                                                  | 4.7              | -   | 1.3       | -   | μs    |                                                       |

| T <sub>HIGH</sub> I <sup>2</sup> C  | HIGH period of the SCL clock                                                                 | 4.0              | -   | 0.6       | -   | μs    |                                                       |

| T <sub>SUSTA</sub> I <sup>2</sup> C | Setup time for a repeated START condition                                                    | 4.7              | -   | 0.6       | -   | μs    |                                                       |

| T <sub>HDDAT</sub> I <sup>2</sup> C | Data hold time                                                                               | 0                | -   | 0         | -   | μs    |                                                       |

| T <sub>SUDAT</sub> I <sup>2</sup> C | Data setup time                                                                              | 250              | -   | 100       | -   | ns    |                                                       |

| T <sub>SUSTO</sub> I <sup>2</sup> C | Setup time for STOP condition                                                                | 4.0              | -   | 0.6       | -   | μs    |                                                       |

| T <sub>BUF</sub> I <sup>2</sup> C   | BUS free time between a STOP and START condition                                             | 4.7              | -   | 1.3       | -   | μs    |                                                       |

| T <sub>SP</sub> I <sup>2</sup> C    | Pulse width of spikes suppressed by the input filter                                         | _                | -   | 0         | 50  | ns    |                                                       |

Figure 2. Definition for Timing for Fast/Standard Mode on the I<sup>2</sup>C Bus

## **Ordering Information**

| Ordering Code  | Package Diagram | Package Type | Operating<br>Temperature |

|----------------|-----------------|--------------|--------------------------|

| CY8C20142-SX1I | 51-85066        | 8 SOIC       | Industrial               |

## Thermal Impedances by Package

| Package | Typical θ <sub>JA</sub> <sup>[7]</sup> |  |  |

|---------|----------------------------------------|--|--|

| 8 SOIC  | 127.22 °C/W                            |  |  |

#### **Solder Reflow Peak Temperature**

| Package | Minimum Peak Temperature <sup>[8]</sup> | Maximum Peak Temperature |

|---------|-----------------------------------------|--------------------------|

| 8 SOIC  | 240 °C                                  | 260 °C                   |

Notes

7. TJ = TA + Power x qJA

8. Higher temperatures may be required based on the solder melting point. Typical temperatures for solder are 220 ± 5°C with Sn-Pb or 245 ± 5°C with Sn-Ag-Cu paste. Refer to the solder manufacturer specifications.

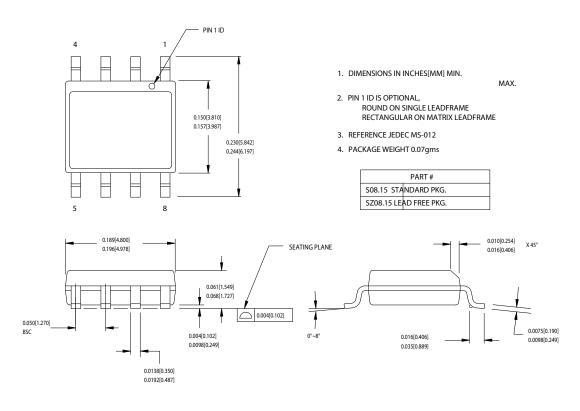

## Package Diagram

Figure 3. 8-Pin (150-Mil) SOIC(51-85066

51-85066-\*C

## **Document History Page**

| Document Title: CY8C20142 CapSense Express™ - 4 Configurable IOs<br>Document Number: 001-32159 |         |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------------------------|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REV.                                                                                           | ECN.    | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| **                                                                                             | 1494145 | TUP/AESA           | New Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *A                                                                                             | 1773608 | TUP/AESA           | Removed table - 3V DC General Purpose IO Specifications<br>Updated Logic Block Diagram<br>Updated table - DC POR and LVD Specifications<br>Updated table - DC Chip Level Specifications<br>Updated table - 5V and 3.3V DC General Purpose IO Specifications<br>Updated table - 2.7V DC General Purpose IO Specifications<br>Updated table - AC GPIO Specifications and split it into two tables for 5V/3.3V and 2.7V<br>Added section on CapSense Express <sup>TM</sup> Software tool |  |

| *B                                                                                             | 2091026 | DZU/MOHD<br>/AESA  | Updated table-DC Chip Level Specifications<br>Updated table-Pin Definitions 16 pin SOIC<br>Updated table-5V and 3.3V DC General Purpose IO Specifications<br>Updated table - 2.7V DC General Purpose IO Specifications<br>Changed definition for Timing for Fast/Standard Mode on the I2C Bus diagram                                                                                                                                                                                 |  |

| *C                                                                                             | 2404731 | DZU/MOHD/PY<br>YRS | Updated Logic Block Diagram<br>Added DC Programming Specifications Table<br>Updated Features<br>Added CapSense Electrical Specifications Table                                                                                                                                                                                                                                                                                                                                        |  |

| *D                                                                                             | 2544918 | ZSK/AESA           | Different sleep modes explained<br>Bi-Directional Sleep Control Pin defined<br>Table added on "2.7V DC Spec for I2C Line with 1.8V External Pull-Up                                                                                                                                                                                                                                                                                                                                   |  |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | <b>PSoC Solutions</b> |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2007-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

#### Document Number: 001-32159 Rev. \*D

#### Revised July 29, 2008

Page 14 of 14

CapSense Express™, PSoC Designer™, Programmable System-on-Chip™, and PSoC Express™ are trademarks and PSoC® is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations. Purchase of I<sup>4</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>4</sup>C Patent Rights to use these components in an I<sup>4</sup>C system, provided that the system conforms to the I<sup>4</sup>C Standard Specification as defined by Philips. All products and company names mentioned in this document may be the trademarks of their respective holders.